张子明,王从庆,刘良勇,王洪涛,黄紫晗

(1.中国人民解放军第5720 工厂 航空设备测控与逆向工程实验室,安徽芜湖 241007;

2.南京航空航天大学自动化学院,江苏南京 211106;

3.芜湖航翼集成设备有限公司,安徽芜湖 241000)

目前,常见的可调电阻是通过手动改变电阻接入电路的长度来改变阻值,例如滑动电阻器和旋钮电位器[1]。这种机械式的可变电阻输出精度低,阻值很难精确控制在特定值,更不容易实现远程控制[2]。而半导体芯片方式的可编程电阻[3-4],通常只有有限的步长和阻值范围,电阻的可用功率也很小,其应用场合受限。目前,基于忆阻器[5]、厚膜电阻[6]等先进技术正在应用于可调电阻器的研究中。

在VI 电路板测试设备阻抗匹配[7-8]、汽车仪表测试台模拟水温和油量变化[9-10]、各种装备部附件设备测试测量[11-12]、配电网单相故障检测[13]、变压器直流偏磁治理[14]等众多场景中,常常需要使用阻值可调的电阻模块,而使用滑动变阻器、电位计等方法无法准确快速给出所需要阻值的电阻,同时手动控制非常不便,无法满足电阻调节自动化要求;

另外使用电子负载需要相应仪器,比较昂贵,所以需要开发一种电路模块实现所需阻值的电阻程控可调。

针对以上分析,提出了一种基于FPGA 的程控可调电阻设计方案,通过FPGA 控制继电器通断,从而进行不同阻值电阻的串联组合,实现输出电阻的连续可调控制。该程控可调电阻模块通过USB 形式的UART 串口与上位机进行通信[15],同时设计了通信帧协议,可接收上位机发送的指令,并输出需要的阻值。

1.1 理论基础

17 世纪至18 世纪,德国数学家莱布尼茨是世界上第一个提出二进制记数法的人[16]。二进制记数只使用0 和1 两个符号,无需其他符号。根据以上思想,任意电阻阻值(整数情况下)可以按二进制分解,用矩阵形式写为:

其中,xn=0 或1,n=1,2,…,N。

数字电子技术以及计算机技术的基本思想正是二进制原理。在数字电子电路中,逻辑门的实现直接应用了二进制,文中模块的设计也使用这个思路。

1.2 实现方法

文中模块的主要实现方法为首先搭建继电器单元,如图1 所示,将编号为1,2,…,N的N个继电器触点分别与1,2,…,2N-1等阻值的N个电阻并联,此时如果控制第n个继电器的控制端为高电平,则继电器吸合,该部分相当于短路,xn=0;

如果控制这个继电器的控制端为低电平,则继电器断开,该部分相当于接入了与其并联的电阻,xn=1。然后再将这些继电器单元串联起来,也就是将各个单元的阻值累加起来,从电子电路的角度实现了式(1)。

图1 继电器单元

2.1 总体框架

程控可调电阻模块以FPGA 为核心主控器件,使用其IO 引脚通过ULN2803 控制1.2 节介绍的继电器单元通断,从而选择需要组合串联的各分立电阻,三个ULN2803 控制三组继电器阵列,每组包括八个继电器单元;

同时,FPGA 还与FT245 的数据、控制、状态等引脚相连,实现FT245 与上位机的数据通信,便于接收上位机发送的电阻设置指令以实现目标阻值的电阻输出。总体框架图如图2 所示,图中的“端子”即为输出电阻端子。

图2 程控可调电阻模块总体框架

2.2 主控器件

主控器件的硬件设计部分采用FPGA 等可编程逻辑器件作为主控器件,利用其IO 资源丰富的特点,通过控制IO 引脚输出高低电平,从而控制继电器的通断,这样就可以使用FPGA 对多个继电器单元进行通断控制;

同时,FPGA 的并行运行机制可以使继电器的控制和动作非常快速,满足了实时性要求。该模块继电器单元共设置24组,可以实现0~16M(224)范围阻值的电阻连续调节设置。

2.3 通信接口

在程控的实现部分,采用FT245 芯片与上位机的USB 口连接,FT245 芯片可以配置成接口形式为USB 的COM 口(串口),这样可以使用PC 机的串口助手向电阻调节模块发送数据,控制电阻调节模块输出相应阻值,便于调试和直观观测。

2.4 驱动隔离

FPGA 的IO 管脚与各电阻相并联的继电器之间选用达林顿管ULN2803 进行驱动,该型号的八路NPN 达林顿连接晶体管阵系列特别适用于低逻辑电平数字电路(诸如TTL、CMOS 或PMOS/NMOS)和较高的电流/电压要求之间的接口,广泛应用于计算机、工业用和消费类产品中的灯、继电器、打印锤或其他类似负载中。所有器件具有集电极开路输出和续流钳位二极管,用于抑制跃变。ULN2803 的设计与标准TTL 系列兼容。

2.5 设计特点

采用以FPGA 为核心的设计可以利用其并行处理的特点,通过对多个继电器的同时控制,实现程控电阻的实时输出。同时利用FPGA 很强的可配置性,实现灵活的应用,例如可以根据实际情况,通过配置的IO 数量确定可调电阻的范围,可使用各种控制器、处理器、FPGA 等通过串口向其发送指令实现程控,而不仅限于PC机,甚至在数据处理要求不高时,由FPGA 自身进行计算无需上位机即可得到需要输出的电阻值。

设计的软件实际为代码化的硬件电路,通过编写硬件描述语言(Verilog HDL)生成FPGA 模块实现预定动作。

3.1 通信协议设计

通信协议协议具有可自行定义的特点,上位机向电阻调节模块发送数据的通信帧设置为:第一个字符为“:”,表示数据帧开始;

第二个字符为阻值十进制的位数;

第三个字符为空格,表示后面的内容为发送的阻值大小;

后面的字符串则为阻值的十进制表示,发送1 000 Ω电阻的数据帧及其说明如表1 所示。

表1 控制阻值为1 000 Ω的数据帧说明

3.2 状态机设计

在FPGA 中的编程采用状态机的思想,根据不同状态采取相应的动作,各个状态的说明如下。

状态0:初始状态。如果接收到“:”字符,则进入状态1;

如果接收到其他字符,则留在状态0。

状态1:接收到字符为“:”后的状态,表示已经接收到数据帧的有效字符。在该状态中,如果接收到数字字符,则进入状态2;

如果接收到“:”字符,则仍留在状态1;

如果接收到其他字符,则进入状态0。

状态2:在状态1后,接收到数字字符后的状态,表示阻值十进制表示情况下的字符串长度。在该状态中,如果接收到空格字符,则进入状态3;

如果接收到“:”字符,则进入状态1;

如果接收到其他字符,则进入状态0。

状态3:在状态2后,接收到空格字符后的状态,表示字符长短与阻值大小字符串之间的间隔。在该状态中,如果接收到数字字符,则进入状态4;

如果接收到“:”字符,则进入状态1;

如果接收到其他字符,则进入状态0。

状态4:在状态3后,接收到数字字符后的状态,表示接收到阻值大小的字符串。在该状态中,如果接收到数字字符,且接收的数字字符串长度未达到应该接收的长度,则留在状态4;

如果接收到“:”字符,则进入状态1;

如果接收到其他字符,或者接收到的数字字符串长度达到应该接收的长度,则进入状态0。

各状态之间的转换关系如图3 所示,接收一帧数据的代码流程如图4 所示。

图3 状态转换关系

图4 接收一帧数据流程

3.3 FT245通信软件设计

3.3.1 时序分析

FT245 的操作时序比较简单,主要分为读取时序和写入时序两个方面,分别发挥读取接收数据和写入发送数据的作用。

1)读取时序

FT245 含一个256 Byte 的接收Buffer,主要用于缓存接收的数据,要读取接收的数据就需要按照图5所示的时序关系将接收Buffer 中的数据提取出来。当RXF 为高时,说明接收FIFO 中无数据或者当前时刻无法读取。所以读取时序的关键是只有当检测到RXF 为低时才可读取,此时控制RD 为低电平,在T3(最多50 ns)时间之后,数据线上的数据方为此次从接收FIFO 中读取的数据。控制RD 为低的时间不少于T1(最少50 ns)。

图5 FT245读取数据时序图

2)写入时序

FT245 含一个128 Byte 的发送Buffer,主要用于缓存将要发送的数据,要写入发送的数据就需要按照图6 所示的时序关系将数据写入发送Buffer 中。当TXE 为低时,说明发送FIFO 中数据已满或者当前时刻无法写入。所以写入时序的关键是只有当检测到TXE 为高时才可写入,此时控制WR 为高电平并保持至少T7时间(50 ns),在WR 回到低电平前T9时间(20 ns)时,数据总线上的数据就是此次写入发送FIFO 的数据。一般而言,为了发送数据更加稳定可靠,在WR 由高电平变为低电平后,数据总线上的数据还应该保持T10时间,而FT245 则不需要该阶段,T10可以为0,这样可以进一步提高数据发送速率。

图6 FT245写入数据时序图

3.3.2 读写模块设计

读写模块内部流程如图7 所示。首先进行初始化,也就是FPGA 一上电或者在接收到复位信号时运行,初始化将FT245 的控制信号设置为无效状态,包括RD 输出高电平,WR 输出低电平,RST_FT 信号输出高电平。另外设置一个标志flag,表示是否有接收到的数据还没有发出(如果有则为1,没有则为0)。

图7 读写模块内部流程

随后按照读取和写入两个部分并行执行,其中读取部分以检测RXF 信号为判断条件,如果检测到RXF 信号为低同时flag 为0,则输出RD 为低电平,读取FT245 接收到的数据。为了稳定可靠,在RXF 为低同时,RD 信号为低电平并保持50 ns 后再读取接收FIFO 中的数据,读取完毕后将这个数据保存并输出RD 为高电平,同时将flag 赋值为1。

写入部分以检测TXE 信号为检测条件,如果检测到TXE 信号为高同时flag 为1时,则将接收到的数据取反并发送出去,将数据放到数据总线上,控制WR 为高电平并保持50 ns,然后将WR 变回低电平,同时将flag 赋值为0。

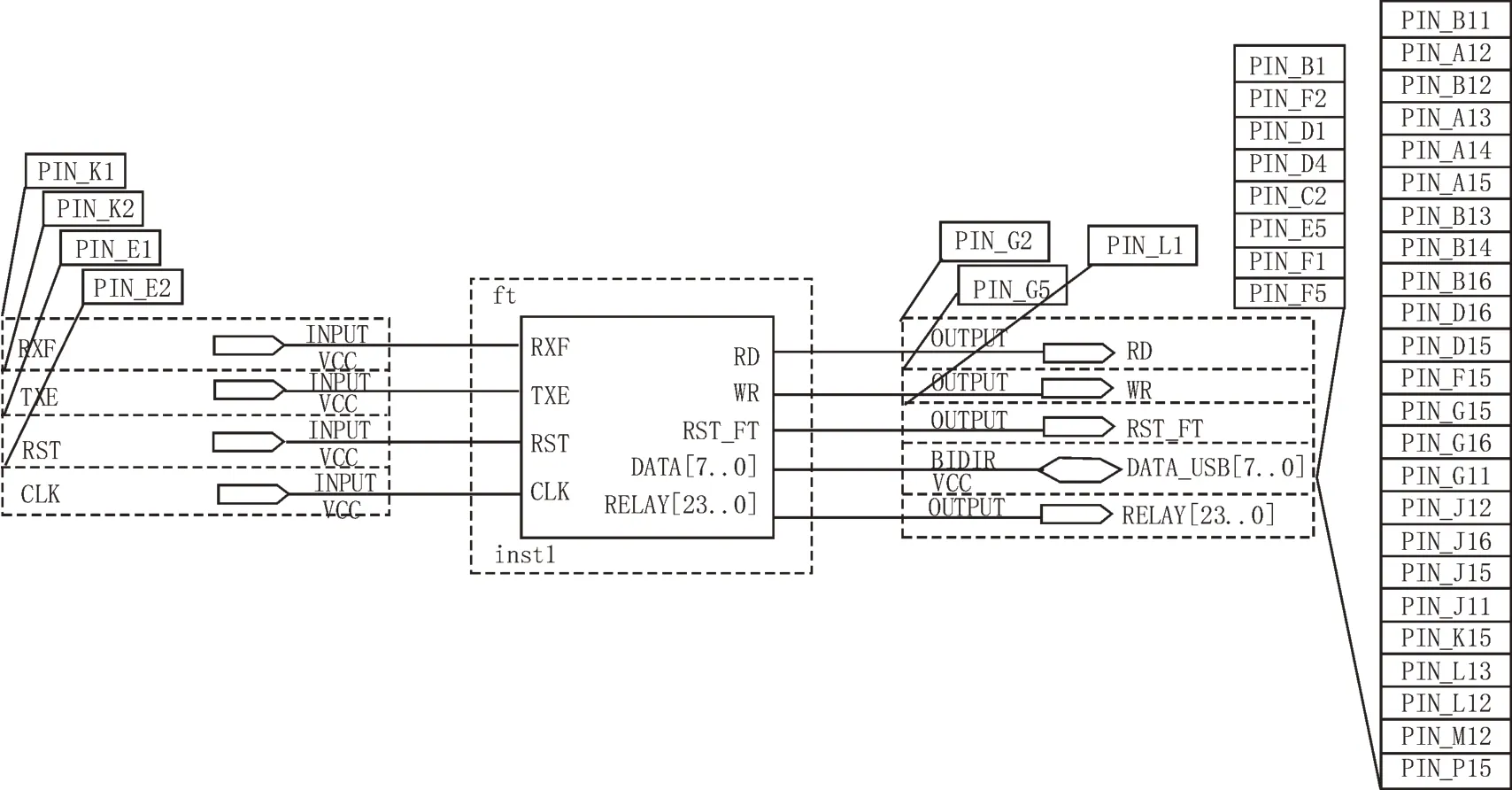

3.4 模块例化

按照以上设计思想综合编写Verilog HDL 代码,并且例化为图8 所示的模块,该模块接收FT245 发送的状态信号,并且对FT245 进行控制和数据的传输,从而实现与上位机的通信。同时该模块内部通过对上位机指令的解析,完成对相应继电器控制IO 的高低电平输出。在该例化的基础上完成对其实际引脚的配置,该模块的引脚说明如表2 所示。

表2 模块引脚说明

图8 模块例化

验证方法为使用串口助手向模块发送3.1 节设计格式的指令,同时使用Hantek365 虚拟万用表对模块进行阻值测量,对比输出的阻值与实际产生阻值,从而对设计的程控电阻模块进行验证。

当设置模块输出1 000 Ω电阻时,通过串口助手发送指令字符串“:4 1000”,继电器动作,万用表测量显示阻值为0.990 kΩ,误差为1.00%。

限于篇幅,多次试验的截图不再给出,综合试验情况,各输出阻值与目标阻值间的误差均在3.00%以下,与常规电阻误差相近,满足大多数应用需要。部分试验及误差情况如表3 所示。

表3 部分试验与误差情况

文中项目研究的程控可调电阻模块可以连续地给出所需要的电阻阻值,可应用于电子负载、在设备中阻抗匹配等场景。试验中出现的误差完全可以满足大部分应用需求,在满足成本要求的情况下,可以通过在每个继电器单元采用更精密的电阻来减小误差。

猜你喜欢 进入状态程控低电平 程控交换机的数据备份与恢复技术分析科技创新导报(2021年33期)2021-04-17基于单片机的程控增益放大器设计电子制作(2019年19期)2019-11-23一种实用的电脑接口判断方法科学与财富(2019年7期)2019-10-212017款凯迪拉克2.8L/3.0L/3.2L/3.6L车型低电平参考电压总线电路图汽车维修技师(2018年7期)2018-12-07基于Multisim10和AD603的程控增益放大器仿真研究电子制作(2018年19期)2018-11-14任务型教学在初中数学中的应用探讨赢未来(2018年33期)2018-04-10数字电子技术的应用电子技术与软件工程(2017年10期)2017-06-02浅谈物理电路与数字电路电子技术与软件工程(2017年2期)2017-03-15国企党员领导干部应当进入状态办公室业务(2016年9期)2016-11-23程控增益射频宽带放大器电子制作(2016年1期)2016-11-07